解析博通硅基光电子高密度CPO关键技术 光电器件篇

随着数据中心对高带宽、低功耗、高密度互连的需求日益迫切,共封装光学(Co-Packaged Optics, CPO)技术正成为下一代高速互连的核心解决方案。在这一前沿领域,博通(Broadcom)凭借其在硅基光电子(Silicon Photonics)领域的深厚积累,推出了一系列高密度CPO关键技术,其中光电器件是构建整个系统的基石。本文将聚焦于博通高密度CPO技术中的关键光电器件,解析其技术特点与创新价值。

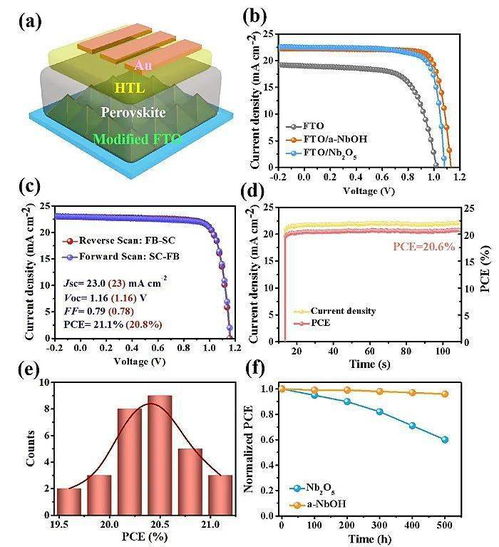

一、 核心光电器件构成:从发射到接收的全链路集成

博通高密度CPO解决方案的核心在于将传统可插拔光模块中的核心光电功能——包括激光器、调制器、光电探测器以及相关的驱动与放大电路——通过先进的封装技术与高性能计算芯片(如ASIC或交换机芯片)紧密集成在同一个基板上或封装内。其关键光电器件链路主要包括:

- 集成激光光源:采用外置或片上集成的高性能、高可靠性激光器作为光信号的源头。博通的技术方案可能涉及高效的光耦合方案,将激光器产生的光高效地引入硅基光波导。

- 高速硅基光调制器:这是硅基光电子的核心优势所在。博通利用硅材料的等离子色散效应,设计并制造出高速、低功耗的硅基马赫-曾德尔干涉仪(MZI)型或微环谐振器型调制器,负责将高速电信号编码到光载波上。其关键技术在于实现高调制效率(低Vπ)、高带宽(支持100Gbaud及以上波特率)以及与CMOS工艺的兼容性。

- 高性能光电探测器:在接收端,采用锗硅(GeSi)或Ⅲ-Ⅴ族材料与硅集成的光电探测器,负责将接收到的光信号高效地转换为电信号。博通致力于提升探测器的响应度、带宽和暗电流性能,以满足高速(如800G、1.6T)系统的苛刻要求。

- 无源光器件网络:包括硅基光波导、光栅耦合器、边缘耦合器、多路复用器/解复用器(Mux/DeMux,如阵列波导光栅AWG)、光功率分束器等。这些器件在硅芯片上实现光信号的传输、分合与路由,其低损耗、高集成度是实现高密度互连的关键。

二、 关键技术突破与创新

博通在实现高密度CPO光电器件方面,展现了多项关键技术突破:

- 高密度异质集成:通过先进的晶圆级键合或芯片贴装技术,将Ⅲ-Ⅴ族激光器、放大器等“非硅”高性能有源器件与标准CMOS工艺制造的硅基光子芯片进行异质集成。这解决了硅本身发光效率低的核心难题,同时保持了硅工艺的集成度和成本优势。

- 共封装设计与热管理:CPO的核心挑战之一是如何将发热量巨大的计算芯片与对温度敏感的光电器件(尤其是激光器)紧密封装在一起。博通在封装架构、散热路径设计、材料选择(如高热导率衬底)等方面进行创新,确保光电器件在复杂热环境下的性能稳定性和长期可靠性。

- 高带宽电光/光电接口:CPO消除了传统可插拔模块与ASIC之间的高速电气接口(如SerDes),但要求光电器件与ASIC之间的电接口具备极高的带宽密度和能效。博通利用其在高性能混合信号电路设计方面的优势,优化了调制器驱动器(Driver)和跨阻放大器(TIA)的设计,实现了更低功耗、更低串扰的短距电互连。

- 系统级封装(SiP)与光耦合:采用先进的2.5D/3D封装技术,将硅光子芯片、电子芯片(ASIC)、中介层(Interposer)等集成在一个封装内。其中,芯片与光纤阵列之间高效、低损耗、高对准容差的光耦合方案(如采用模斑转换器或透镜系统)是保障系统性能和生产可行性的关键。

三、 应用前景与挑战

博通的硅基光电子高密度CPO光电器件技术,主要瞄准超大规模数据中心、人工智能/机器学习集群、高性能计算等需要极高内部带宽的应用场景。它能显著降低系统功耗(消除SerDes功耗)、提升带宽密度、减小延迟和物理尺寸。

该技术走向大规模商用仍面临挑战:包括复杂的封装工艺带来的成本问题、产业链成熟度、测试与维修的难度,以及需要与生态系统(交换机芯片厂商、系统制造商)建立更紧密的协同设计流程。

总而言之,博通在高密度CPO领域的光电器件技术,代表了硅基光电子与先进封装技术融合的前沿方向。通过核心有源/无源器件的创新设计、异质集成和系统级封装优化,博通正致力于解决高速互连的能耗与密度瓶颈,为下一代数据基础设施奠定坚实的光电硬件基础。随着技术的不断成熟和成本的优化,CPO有望在未来五年内从前沿技术走向主流应用。

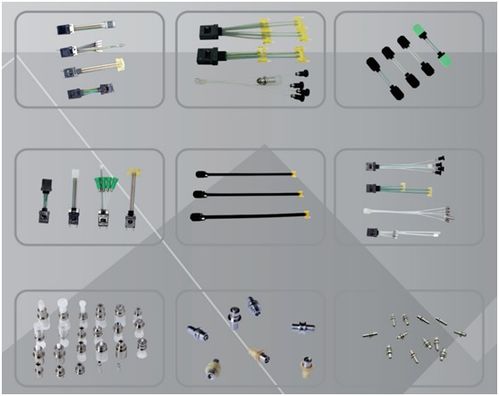

最新产品